En trigger er et element i digital teknologi, en bistabil enhet som bytter til en av tilstandene og kan forbli i den på ubestemt tid selv når eksterne signaler fjernes. Den er bygget fra logiske elementer på det første nivået (AND-NOT, OR-NOT, etc.) og tilhører de logiske enhetene på det andre nivået.

I praksis produseres flip-flops i form av mikrokretser i en separat pakke eller inngår som elementer i store integrerte kretser (LSI) eller programmerbare logiske arrays (PLM).

Innhold

Klassifisering og typer triggersynkronisering

Triggere faller inn i to brede klasser:

- asynkron;

- synkron (klokket).

Den grunnleggende forskjellen mellom dem er at for den første kategorien enheter endres utgangssignalnivået samtidig med endringen i signalet ved inngangen (inngangene).For synkrone triggere skjer en tilstandsendring bare hvis det er et synkroniseringssignal (klokke, strobe) ved inngangen som er gitt for dette. For dette er det gitt en spesiell utgang, betegnet med bokstaven C (klokke). I henhold til typen port er synkrone elementer delt inn i to klasser:

- dynamisk;

- statisk.

For den første typen endres utgangsnivået avhengig av konfigurasjonen av inngangssignalene på tidspunktet for utseendet til fronten (forkant) eller fallet av klokkepulsen (avhengig av den spesifikke typen trigger). Mellom utseendet til synkroniseringsfronter (hellinger), kan alle signaler påføres inngangene, tilstanden til utløseren vil ikke endres. I det andre alternativet er tegnet på klokke ikke en endring i nivå, men tilstedeværelsen av en eller null ved klokkeinngangen. Det er også komplekse triggerenheter klassifisert etter:

- antall stabile tilstander (3 eller flere, i motsetning til 2 for hovedelementene);

- antall nivåer (også mer enn 3);

- andre egenskaper.

Komplekse elementer er av begrenset bruk i spesifikke enheter.

Typer triggere og hvordan de fungerer

Det finnes flere grunnleggende typer triggere. Før du forstår forskjellene, bør en felles egenskap bemerkes: når strøm tilføres, settes utgangen til en hvilken som helst enhet til en vilkårlig tilstand. Hvis dette er kritisk for den generelle driften av kretsen, må forhåndsinnstillingskretser leveres. I det enkleste tilfellet er dette en RC-krets som genererer et signal for innstilling av starttilstand.

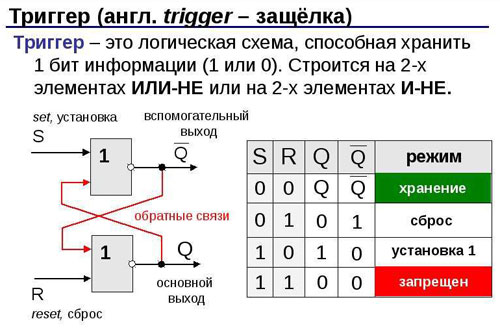

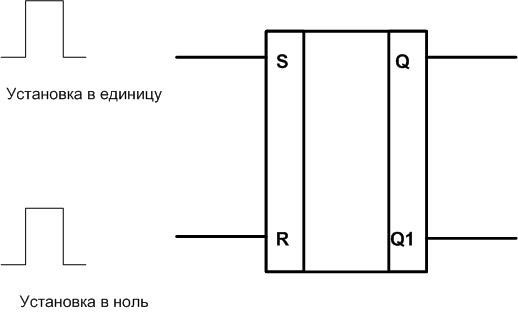

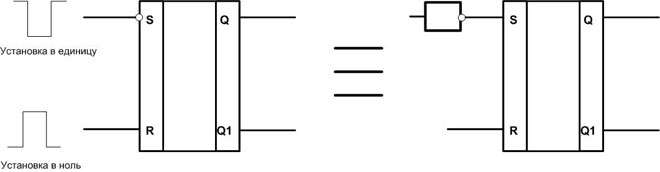

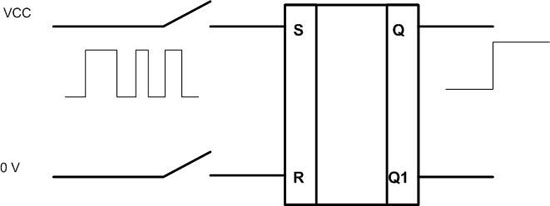

RS flip-flops

Den vanligste typen asynkron bistabil enhet er RS flip-flop. Det refererer til flipflops med separat innstilling av tilstand 0 og 1.Det er to innganger for dette:

- S - sett (installasjon);

- R - tilbakestill (tilbakestill).

Det er en direkte utgang Q, det kan også være en invertert utgang Q1. Det logiske nivået på den er alltid det motsatte av nivået på Q - dette er nyttig når du designer kretser.

Når et positivt nivå påføres inngangen S, vil utgangen Q bli satt til en logisk enhet (hvis det er en invertert utgang, vil den gå til nivå 0). Etter det, ved inngangen til oppsettet, kan signalet endres som du vil - dette vil ikke påvirke utgangsnivået. Inntil en 1 vises ved inngangen R. Dette vil sette flip-flop til tilstand 0 (1 på den inverterte utgangen). Å endre signalet ved tilbakestillingsinngangen vil ikke påvirke elementets videre tilstand.

Viktig! Alternativet når det er en logisk enhet ved begge innganger er forbudt. Utløseren vil bli satt til en vilkårlig tilstand. Ved utforming av ordninger bør denne situasjonen unngås.

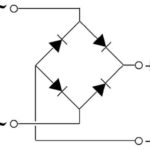

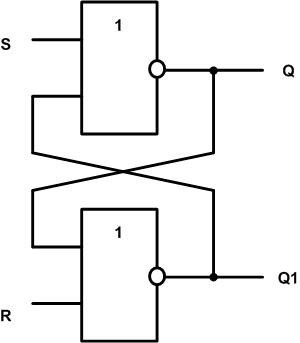

En RS-flip-flop kan bygges på grunnlag av mye brukte NAND-elementer med to innganger. Denne metoden er implementert både på konvensjonelle mikrokretser og inne i programmerbare matriser.

En eller begge innganger kan inverteres. Dette betyr at på disse pinnene styres utløseren av utseendet til ikke et høyt, men et lavt nivå.

Hvis du bygger en RS-flip-flop på AND-NOT-elementer med to innganger, vil begge inngangene være inverse - kontrollert av tilførselen av en logisk null.

Det er en gated versjon av RS flip-flop. Den har en ekstra inngang C. Bytting skjer når to betingelser er oppfylt:

- tilstedeværelsen av et høyt nivå ved Set- eller Reset-inngangen;

- tilstedeværelsen av et klokkesignal.

Et slikt element brukes i tilfeller der vekslingen må forsinkes, for eksempel ved slutten av transienter.

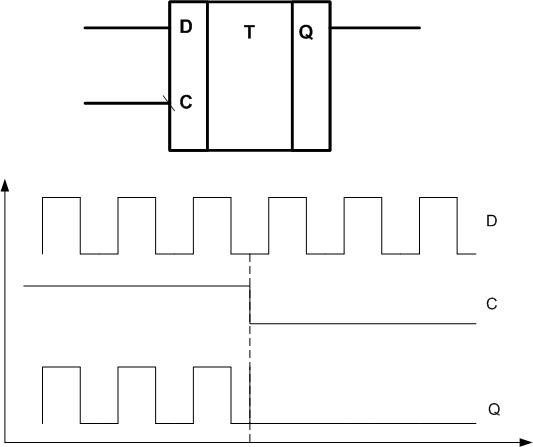

D flipflops

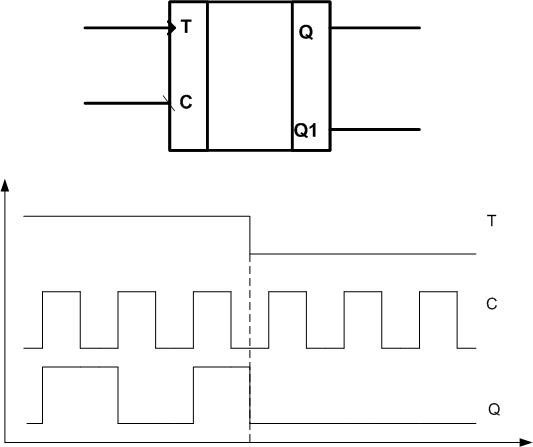

D-trigger ("transparent trigger", "latch", latch) tilhører kategorien synkrone enheter, klokket av inngang C. Det er også en datainngang D (Data). Når det gjelder funksjonalitet, tilhører enheten triggere med mottak av informasjon gjennom én inngang.

Så lenge en logisk er tilstede ved klokkeinngangen, gjentar signalet ved utgangen Q signalet ved datainngangen (transparensmodus). Så snart strobenivået går til tilstand 0, vil nivået på utgangen Q forbli det samme som det var på tidspunktet for kanten (låsene). Så du kan fikse inngangsnivået ved inngangen når som helst. Det er også D-flip-flops med klokke på fronten. De låser signalet på den positive kanten av blitzen.

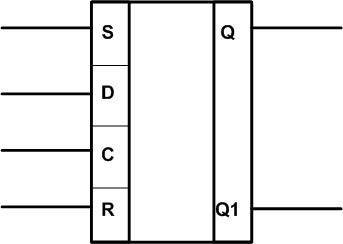

I praksis kan to typer bistabile enheter kombineres i en mikrokrets. For eksempel D og RS flip-flop. I dette tilfellet har Set/Reset-inngangene prioritet. Hvis det er en logisk null på dem, oppfører elementet seg som en vanlig D-flip-flop. Når et høyt nivå forekommer på minst én inngang, settes utgangen til 0 eller 1, uavhengig av signalene på inngangene C og D.

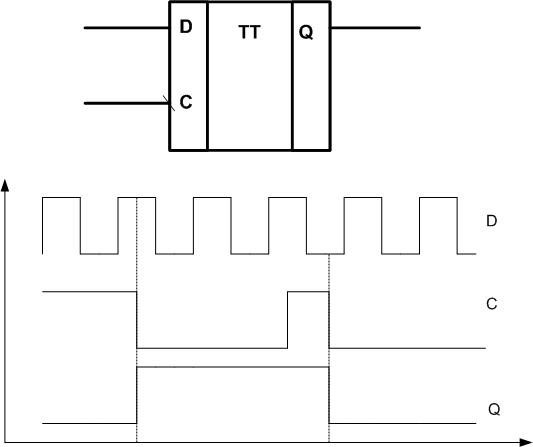

Gjennomsiktigheten til en D-flip-flop er ikke alltid en nyttig funksjon. For å unngå det, brukes doble elementer (flip-flop, "klappende" utløser), de er merket med bokstavene TT. Den første utløseren er en vanlig lås som sender inngangssignalet til utgangen. Den andre utløseren fungerer som et minneelement. Begge enhetene klokkes med én strobe.

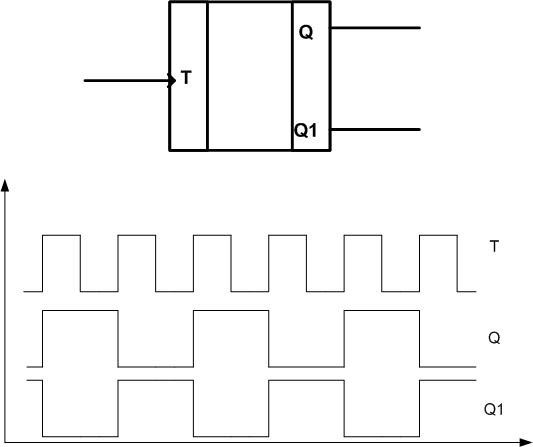

T-flip-flops

T-triggeren tilhører klassen av tellbare bistabile elementer. Logikken i arbeidet er enkel - den endrer tilstand hver gang den neste logiske enheten kommer til input.Hvis et pulssignal tilføres inngangen, vil utgangsfrekvensen være dobbelt så høy som inngangen. Ved den inverterte utgangen vil signalet være ute av fase med den direkte.

Dette er hvordan en asynkron T-flip-flop fungerer. Det er også et synkront alternativ. Når et pulssignal påføres klokkeinngangen og i nærvær av en logisk enhet ved utgangen T, oppfører elementet seg på samme måte som et asynkront - det deler inngangsfrekvensen i to. Hvis T-pinnen er logisk null, er Q-utgangen satt lav, uavhengig av tilstedeværelsen av strober.

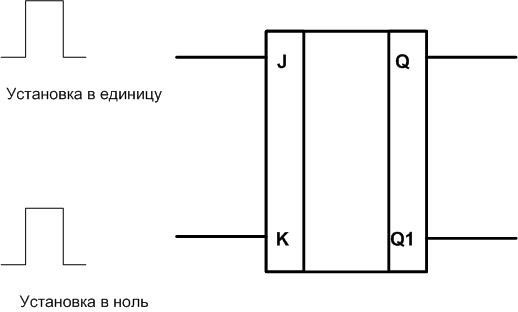

JK flip-flops

JK flip-flops

Dette bistabile elementet tilhører kategorien universelle. Den kan styres separat av innganger. Logikken til JK flip-flop ligner på arbeidet til RS-elementet. J (Job)-inngangen brukes til å sette utgangen til én. Et høyt nivå på K (Keep)-pinnen tilbakestiller utgangen til null. Den grunnleggende forskjellen fra RS-triggeren er at samtidig opptreden av ener på to kontrollinnganger ikke er forbudt. I dette tilfellet endrer utgangen av elementet sin tilstand til det motsatte.

Hvis Job- og Keep-utgangene er koblet til, blir JK-flip-flop til en asynkron tellende T-flip-flop. Når en firkantbølge påføres den kombinerte inngangen, vil utgangen være halve frekvensen. I likhet med RS-elementet, er det en klokket versjon av JK flip-flop. I praksis er det hovedsakelig gatede elementer av denne typen som brukes.

Praktisk bruk

Egenskapen til triggere for å beholde den registrerte informasjonen selv når eksterne signaler fjernes, gjør at de kan brukes som minneceller med en kapasitet på 1 bit.Fra enkeltelementer kan du bygge en matrise for lagring av binære tilstander - i henhold til dette prinsippet bygges statiske tilfeldige tilgangsminner (SRAM). En funksjon ved et slikt minne er en enkel krets som ikke krever ekstra kontrollere. Derfor brukes slike SRAM-er i kontrollere og PLA-er. Men den lave opptakstettheten forhindrer bruk av slike matriser i PC-er og andre kraftige datasystemer.

Bruken av flip-flops som frekvensdelere ble nevnt ovenfor. Bistabile elementer kan kobles i kjeder og få ulike delingsforhold. Den samme strengen kan brukes som pulsteller. For å gjøre dette er det nødvendig å lese tilstanden til utgangene fra de mellomliggende elementene i hvert øyeblikk - en binær kode vil bli oppnådd som tilsvarer antall pulser som kom til inngangen til det første elementet.

Avhengig av typen triggere som brukes, kan tellere være synkrone eller asynkrone. Serie-til-parallell-omformere er bygget etter samme prinsipp, men kun gatede elementer brukes her. Også digitale forsinkelseslinjer og andre elementer av binær teknologi er bygget på triggere.

RS flip-flops brukes som nivåklemmer (sprettdempere). Hvis mekaniske brytere (knapper, brytere) brukes som logiske nivåkilder, vil spretteffekten danne mange signaler i stedet for ett. RS flip-flop kjemper med suksess mot dette.

Omfanget av bistabile enheter er bredt. Utvalget av oppgaver som løses med deres hjelp avhenger i stor grad av fantasien til designeren, spesielt innen ikke-standardiserte løsninger.

Lignende artikler: